## 2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8=50, will be treated as malpractice. Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

## Sixth Semester B.E. Degree Examination, Jan./Feb. 2023 **Microelectronics Circuits**

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, selecting atleast THREE questions from Part-A and any TWO questions from Part-B.

## PART – A

- Derive the expression for i<sub>D</sub> in saturation and triode region with the neat diagram. Explain 1 the effect of increase in drain to source voltage after saturation. (10 Marks)

- Why large signal model is required? Explain the large signal model of NMOS. (04 Marks)

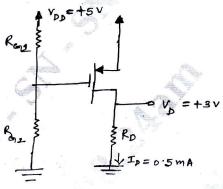

- Determine the value of R<sub>D</sub>, which is required for maintaining saturation region for the following circuit. The transistor operates in saturation with  $I_D = 0.5$ mA and  $V_D = +3$ V. Let the enhancement type PMOS transistor have  $v_t$  = -1V and  $K_n'(W/L)$  = 1mA/m² and assume  $\lambda = 0$ . (06 Marks)

Fig.Q.1(c)

- Explain the effect of denegative resistance in biasing by fixing V<sub>G</sub> and connecting resistance 2 in the source. Compare the other biasing.

- What is source follower? Derive the voltage gain and overall voltage equations of a source (10 Marks) follower using MOSFET.

- Mention any 4 comparison of important characteristics of MOSFET and the BJT. (04 Marks) 3

- b. Explain different types of short channel in scaling MOSFET. (06 Marks)

- Draw the MOSFET constant current source circuit and explain it along with advantage.

(10 Marks)

- Explain the operation of a MOS cascade amplifier. Mention its advantage and obtain an expression for short circuit trans conductance GM. (10 Marks)

- Derive the voltage gain expression for CMOS implementation of CS amplifier. (10 Marks) b.

- Show that CMRR of perfectly matched MOS differential amplifier with a common mode 5 input signal V<sub>icm</sub> is infinite. (10 Marks) (10 Marks)

- Explain the basic MOS differential pair operation.

## PART - B

- 6 a. Explain four basic feedback topologies with neat diagram.

b. Explain briefly with expression the properties of negative feedback.

c. Draw general structure of feedback amplifier.

(08 Marks)

(08 Marks)

(08 Marks)

- 7 a. Why non inverting configuration of Op-amp is called as voltage follower amplifier. Explain the operation with equivalent circuit model. (06 Marks)

- b. Show that CMRR of a single Op-amp difference amplifier is finite. (10 Marks)

- c. Discuss the effect of finite open-loop gain of an inverting configuration of Op-amp.

(04 Marks)

- 8 a. Explain the parameters required to characterize the operation and performance of logic circuit family. (10 Marks)

- b. Implement  $F = \overline{AB + CD}$  using the AOI Gate. (06 Marks)

- c. Write the circuit for a two-input CMOS NOR gate and a two-input CMOS NAND gate.

(04 Marks)